About Me

I’m Karthik Yadav, a final-year Computer Science student at VIT Vellore (graduating July 2026, CGPA 8.03/10). I work on applied ML, quantitative finance, and low-latency systems.

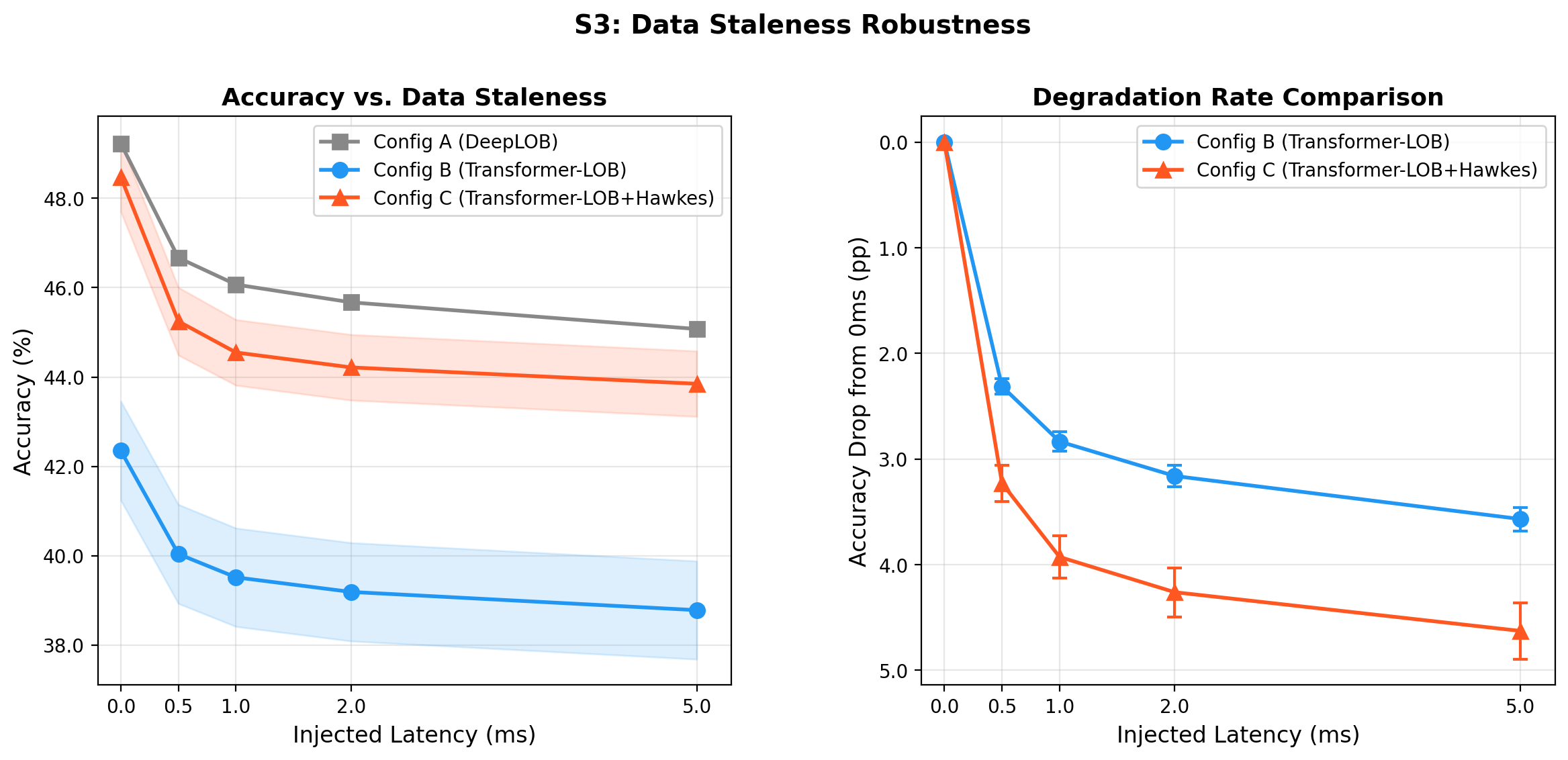

My recent work focuses on microstructure prediction for high-frequency trading. I built a Transformer architecture that fuses limit order book state with Hawkes process intensity features, achieving +6.13pp over baseline (p<0.0001). That work was accepted as a first-author paper at AIAI 2026 (Springer LNCS).

Outside of research, I build things in C++ and Go and play badminton regularly.

Publications

2026

AIAI 2026 — First Author

When Not to Trade: Hawkes Intensity Burst Detection for Regime-Aware Limit Order Book Prediction. Cross-attention Transformer fusing LOB state with Hawkes process features; +6.13pp accuracy over baseline (p<0.0001).

2025

ICECMSN 2025 — Co-author

Energy-efficient multi-hop communication protocol for wireless sensor networks, improving network coverage by 30%.

2026

OTCON 5.0 — Co-author

AI-powered interview platform using RAG architecture with Google Gemini LLM.

Education

Sep 2022 - Jul 2026

B.Tech in Computer Science and Engineering

Vellore Institute of Technology, Vellore

GPA:

8.03 / 10

Projects

PyTorch

C++

Numba

ONNX

Hawkes + Transformer LOB Prediction

Deep learning system fusing limit order book state with Hawkes process intensity features for high-frequency mid-price prediction. +6.13pp over baseline (p<0.0001).

C++

Go

PostgreSQL

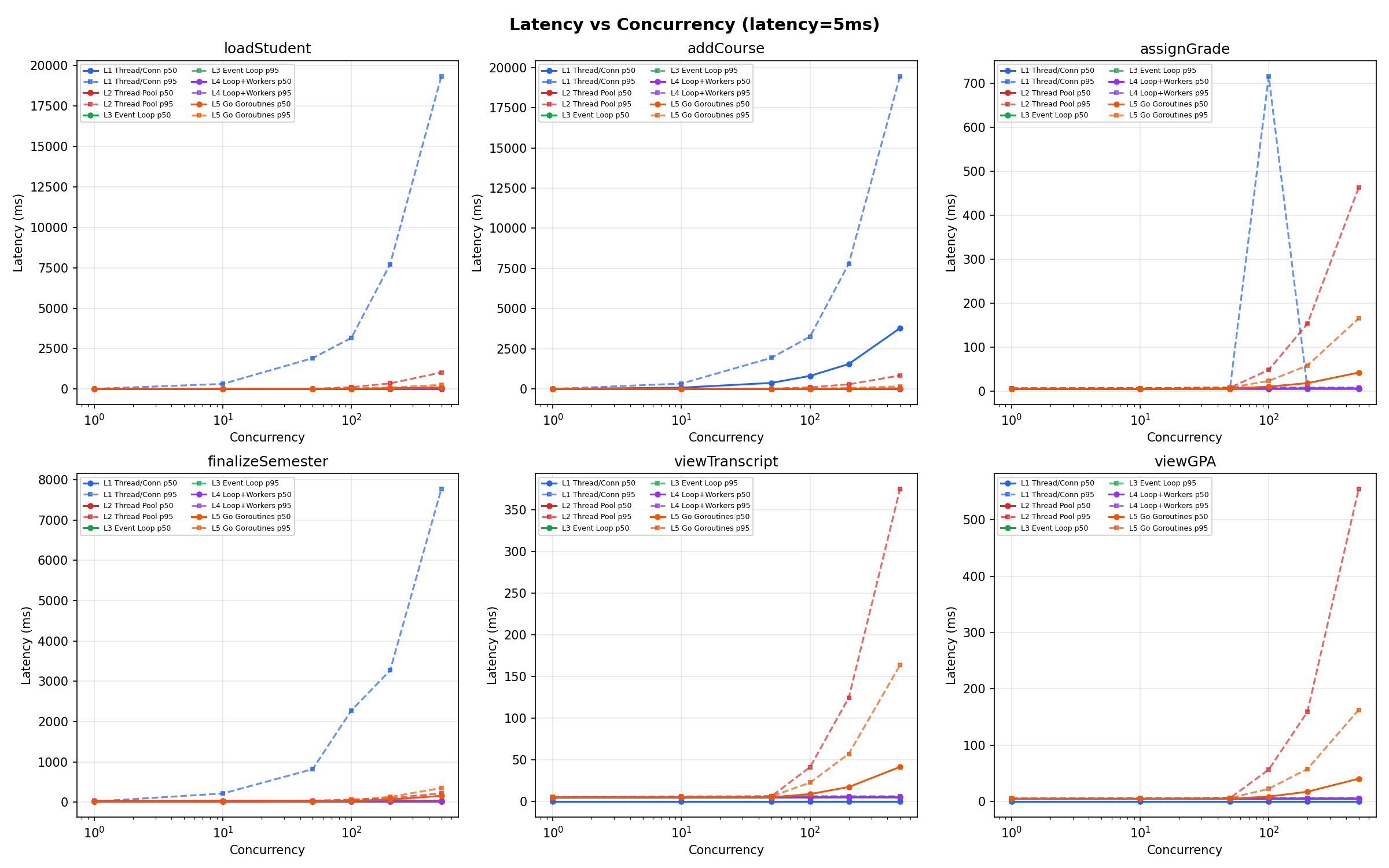

Concurrency Benchmark Engine

Multi-level C++ and Go benchmark comparing five concurrency architectures against PostgreSQL with TCP latency injection via macOS dummynet.